流水线技术

流水线-概念

相关参数计算:流水线执行时间计算。流水线吞吐率、流水线加速比、流水线效率

流水线是指在程序执行时多条指令重叠进行操作的一种准并行处理实现技术。各种部件同时处理屎针对不同指令而言的,它们可同时为多条指令的不同部分进行工作,以提高各部件的利用率和指令的平均执行速度

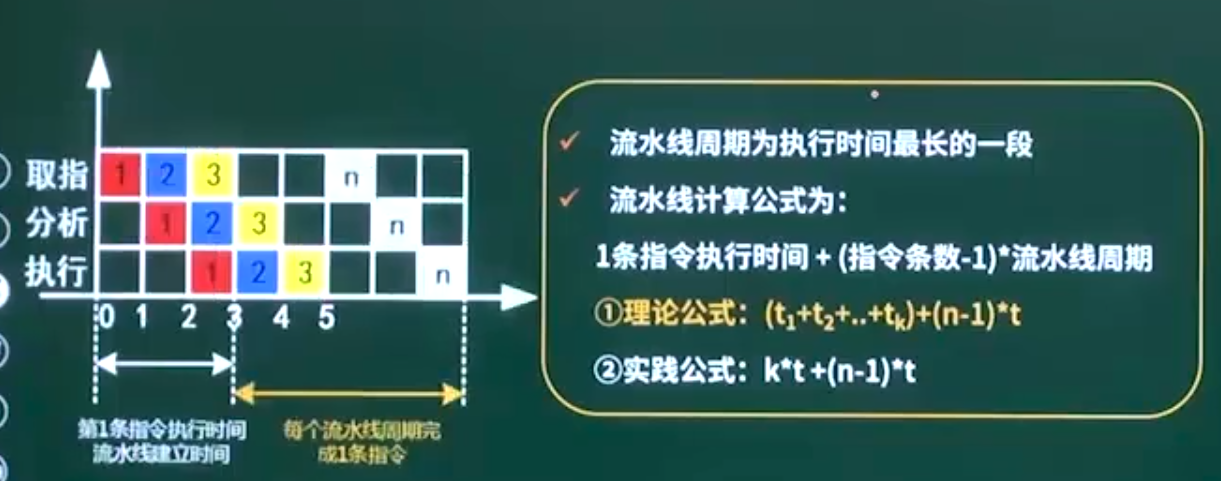

流水线-流水线计算

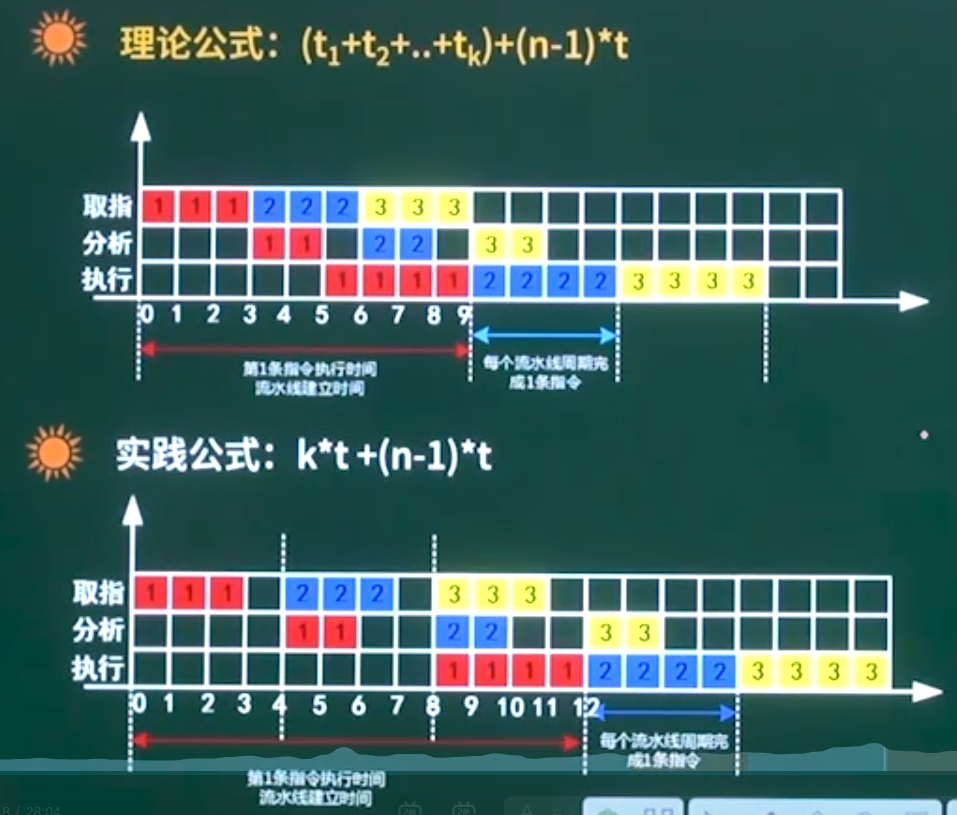

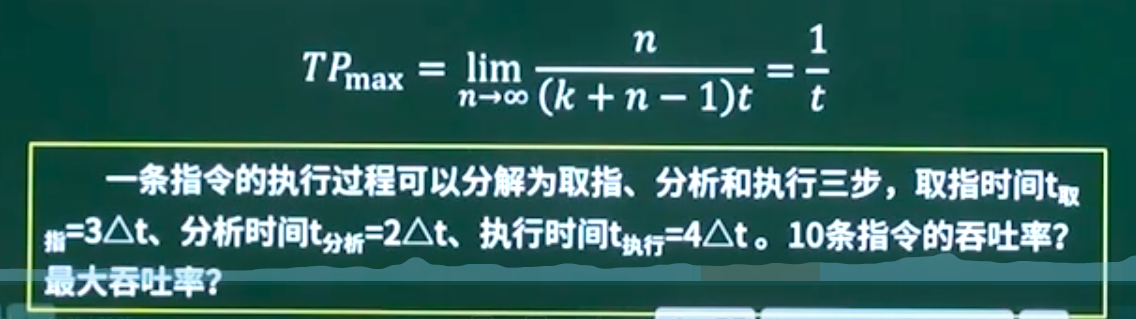

一条指令的执行过程可以分解为取指、分析和执行三步,在取指时间$t_{取指}$=3$\Delta$t、分析时间$t_{分析}$=2${\Delta}$t、执行时间$t_{执行}$=4${\Delta}$t的情况下,若按串行方式执行,则10条指令全部执行完需要()${\Delta}$t;若按流水线的方式执行,流水线周期为()${\Delta}$t,则10条指令全部执行完需要()${\Delta}$t。

流水线 - 流水线吞吐率计算

流水线的吞吐率(Though Put rate, TP)是指在单位时间内流水线所完成的任务数量或输出的结果数量。计算流水线吞吐率的最基本的公式如下:

TP=$\frac{指令条数}{流水线执行时间}$

流水线最大吞吐率:

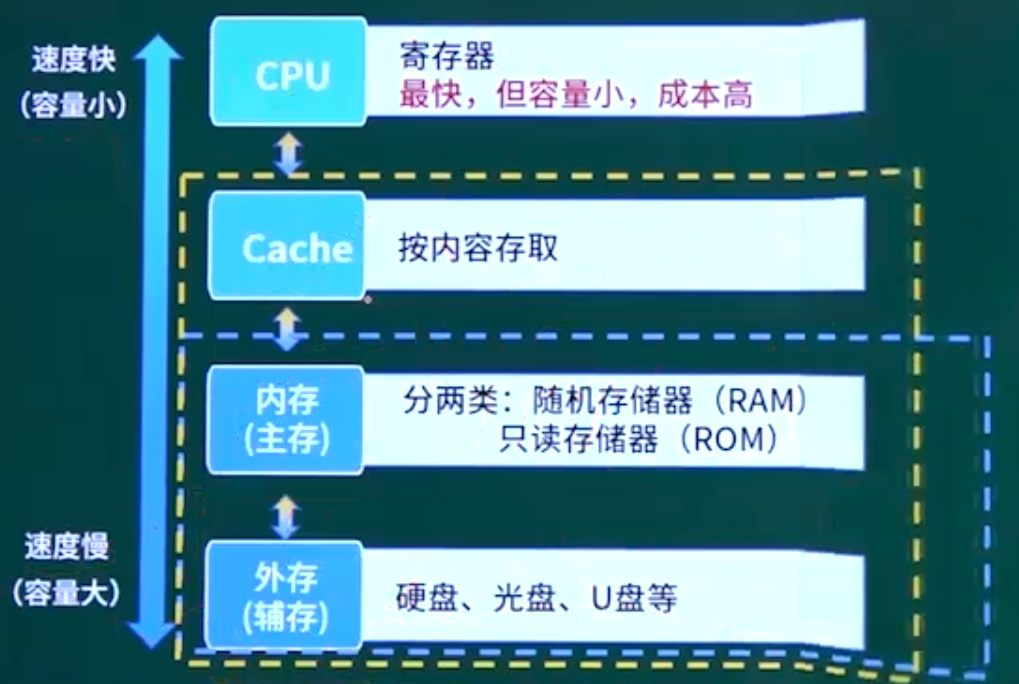

存储系统

考点1:层次化存储体系

考点2:Cache

考点3: 主存编址计算

考点1:层次化存储结构

局部性原理是层次化存储结构的支持

时间局部性:刚被访问的内容,立即又被访问。

空间局部性:刚被访问的内容,临近的空间很快的被访问。

层次化存储结构-分类

1、存储器位置

内存&外存

2、存取方式

(1)按内容存取:

相关存储器(如Cache)

(2)按地址存取

随机存取存储器(如内存)

顺序存取存储器(如磁带)

直接存取存储器(如磁盘)

3、工作方式

(1)、随机存取存储器RAM(如内存DRAM)

(2)、只读存储器ROM(如BIOS)

DRAM:动态随机存取存储器

SRAM:静态随机存取存储器

Cache:高速缓存

EEPROM:电可擦可编程只读存储器

考点2:Cache

Cache-概念

在计算机的存储系统体系中,Cache是访问速度最快的层次(若有寄存器,则寄存器最快)。

使用CaChe改善系统性能的依据是程序的局部性原理

时间局部性

空间局部性

- 如果以h代表对Cache的访问命中率,$t_1$表示Cache的周期时间,$t_2$表示主存储器周期时间,以读操作为例,使用“Cache+主存储器”的系统的平均周期为$t_3$,则:

$t_3$=h$$$t_1$+(1 - h)$$$t_2$

其中,(1- h)又称为失效率(未命中率)。

- 直接相联映像:硬件电路较简单,但冲突率很高。

- 全相联映像: 电路难于设计和实现,只适用于小容量的cache,冲突率较低。

组相联映像:直接相联与全相联的折中

注:主存与Cache之间的地址映射由硬件直接完成

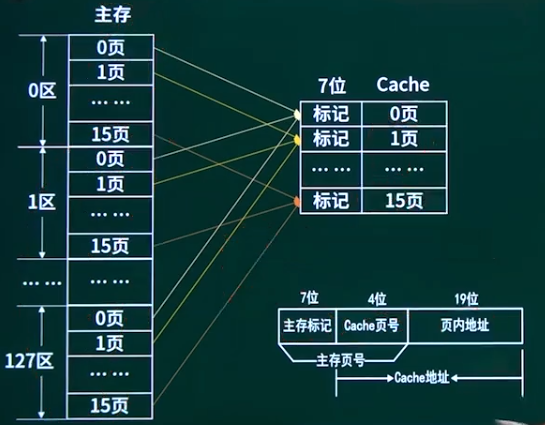

Cache - 映像

- 地址映像是将主存与Cache的存储空间划分为若干大小相同的页(或称为块)。

例如,某机的主存容量为1GB,划分为2048页,每页512KB;Cache容量为8MB,划分为16页,每页512KB。

Cache - 直接相联映像

Cache - 全相联映像

特点:冲突率低,电路复杂

Cache - 组相联映像

Cache - 映像

| 冲突率(高、中、低) | 电路复杂度(复杂、简单、折中) | |

|---|---|---|

| 直接相联映像 | 高 | 简单 |

| 全相联映像 | 低 | 复杂 |

| 组相联映像 | 中 | 折中 |

考点3: 主存编址计算

主存 - 编址

主存 - 编址与计算

- 存储单元

存储单元个数=最大地址 - 最小地址 + 1

- 编址内容

按字编址:存储体的存储单元是字存储单元,即最小寻址单位是一个字。

按字节编址:存储体的存储单元是字节存储单元,即最小寻址单位是一个字节。

- 总容量 = 存储单元个数 * 编址内容

根据存储器所要求的内容和选定的存储芯片的容量,就可以计算出所需芯片的总数,即:

总片数 = 总容量 / 每片的容量